# VLSI Design of a Novel BOSR Architecture for High Speed Applications

Pari A.Labhe<sup>1</sup>

K.Jamal<sup>2</sup>

M.Kiran<sup>3</sup>

D.Jayanthi<sup>4</sup>

labhe\_pari@yahoo.co.in<sup>1</sup> kjamal24@gmail.com<sup>2</sup> kiran\_m\_20@rediffmail.com<sup>3</sup> jayanthivlsi@gmail.com<sup>4</sup> <sup>1</sup>PG Scholar, Gokaraju Rangaraju Institute of Engineering & Technology, Bachupally, Kukatpally,

Hyderabad.

<sup>2</sup>Associate Professor,Dept. of ECE, Gokaraju Rangaraju Institute of Engineering & Technology, Bachupally, Kukatpally, Hyderabad.

<sup>3</sup>Associate Professor, Dept. of ECE, Gokaraju Rangaraju Institute of Engineering & Technology, Bachupally, Kukatpally, Hyderabad.

<sup>4</sup>Professor,Dept. of ECE, Gokaraju Rangaraju Institute of Engineering & Technology, Bachupally, Kukatpally, Hyderabad.

Abstract— Abundance repair is a conventionally used methodology for memory yield change. Remembering the true objective to ensure high repair rate and last thing yield, it is critical to develop a repair scheme for the coming three-dimensional (3D) plan of stacked DRAM. According to the JEDEC flexible memory development manage, the interface of 3D DRAM, including the Wide I/O and High-Bandwidth Memory (HBM), is mainly appointed channelbased memories. In this paper, we propose a worked off individual test (BOSR) scheme at the controller level for channel-based 3D memory to enhance last thing yield after the holding of a memory 3D shape to its relating basis pass on. The method of reasoning fail miserably contains the Channel controller, in which the BOSR circuit stays. Test when occurred exhibits that the repair rate is high with higher gathering dissatisfaction extent on account of the versatile count we pick. The zone overhead is low and it decreases out and out when the memory size or channel count increases. The execution discipline is similarly low due to the parallel execution of address examination and repair. Moreover, the formation cost is lower than customary DRAM plan on account of allocator-based redundancies. Finally, the proposed plan can without a doubt be associated with other channel-based 3D memories.

# I. INTRODUCTION

As semiconductor memory headway keeps moving, the thickness and cutoff of memory gadgets continue expanding in a general sense. This is true blue for presented recollections also, it is comprehended in

[2] that for a typical framework on-chip (SOC), implanted memory parts are having around 90% of the bomb hopelessly district, charging the SOC yield. For a standard SOC, enhancing the yield of installed recollections changes into the key of SOC yield change. For a 3D memory-premise stack, the yield of both the memory flop frightfully and reason pass on must be satisfactorily high, or the stacked 3D IC will be excessively costly, making it hard to make. Able memory test and repair approaches along these lines are critical. Present day thing recollections are normally furnished with wealth, used to repair broken parts of the memory. Different repair frameworks for standard recollections have been examined and announced [3]. A parallel certain individual test (BIST) for various repairable memory centers with various sizes and serial repair fragment was proposed [4]. A characteristic selfrepair (BISR) approach utilizing parallel sub-analyzer in context of web based testing which can drive forward through hard misunderstandings was propose [5].

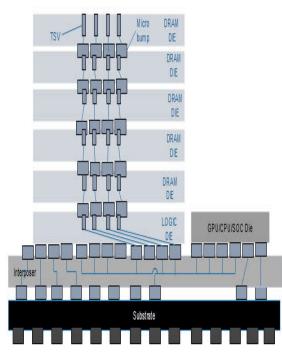

A reconfigurable BISR plot for various RAM sizes and reiteration setups was appeared [6]. Different other BISR outlines and repair structures are proposed [6-10]. Likewise, beginning late, there are packs of techniques proposed for 3D memory stacks appeared in Fig. 1 [1]. A large portion of them concentrated on the specific redundancies of the DRAM kicks the bowl. For instance, a baddie reusing philosophy was proposed to overhaul the yield of memory stack with through silicon

by strategies for (TSV) interconnects. A between flop terribly sharing emphasis plan which connects with the excess of one kick the compartment of a 2-bomb hopelessly stacked RAM to be utilized by the other bomb pitiably was proposed to broaden the adaptability of the redundancies. Another comparative work to organize plenitude sharing crosswise over got done with neighboring passes on was proposed for the memory stacks with in excess of two kicks the can. Also, the layer excess idea was presented, what's more, the differentiating yield change was assessed and an informative model. Some more BISR plans and repair techniques for 3D stacked recollections are broke down. In any case, so far the BISR plan particularly for channel-based 3D memory is yet to be analyzed.

Fig. 1. Generalist 3D memory architecture. [1]

## **II. 3D MEMORY CHARACTERISTICS**

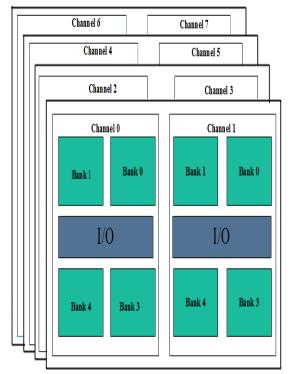

As appeared by the judgments of the HBM, Hybrid Memory Cube (HMC), and Wide I/O DRAM [11], these memory blueprints can be named channel-based DRAM. As appeared in Fig. 2, channel-based recollections are streamlined for high-data trade confine errand to a load of different DRAM contraptions over various self-decision interfaces called channels. As appeared in Fig. 2, each channel offers access to a strategy of DRAM puts money on a kick the can in the stack. The channels can be gotten to freely and at the

same time. The memory stack is ordinarily connected with a technique for thinking bomb unpleasantly, which may contain circuit modules, for example, memory controller, ECC, BIST/BISR, et cetera.

Fig. 2 .A channel-based architecture for DRAM memory stack. [1]

# III. PROPOSED REDUNDANCY REPAIR SCHEME

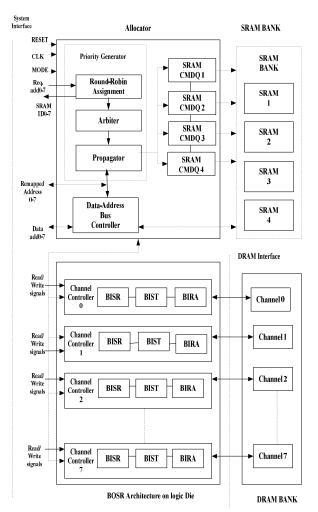

We expect that the individual DRAM kicks the bowl are known extraordinary flops hopelessly (KGDs), i.e., they have been endeavored and repaired (if fundamental) on wafers utilizing standard laser or e-combine repair outlines. In any case, 3D-DRAM in context of TSV improvement and more diminutive scale pounding may incite additional deformities after DRAM kick the bowl stacking and holding. In what tails we propose a repairing plan for the DRAM stack, focusing on these additional imperfections. We propose a repairing outlining called BOSR to make the redundancies all the more competently allocated in light of the particulars of channels. To accomplish this, we section the BOSR plot on the premise bomb hopelessly into three regions: Redundancies (SRAM modules), channel controllers with BISR module (one for each channel), and an Allocator.

Fig. 3. Square chart of the proposed BOSR engineering, accepting four SRAM modules and eight

Channel controllers with BISR modules that are

balanced associated with eight DRAM channels. The square outline of the proposed BOSR arrangement is appeared in Fig. 3. An eight-channel DRAM square is on the advantage with the repairing circuits on the left. Each channel has its given Channel controller with BISR module, and the Channel controllers can keep running in parallel. The SRAM modules on the legitimization flop terribly are utilized as redundancies. The Allocator is utilized to consign the SRAM modules in test mode and virtuoso the SRAM module gets to in common mode. Note that the measure of SRAM modules isn't for the most part the same with the measure of channels. It is settled in light of the surveyed distortion thickness and blemish disseminating of the thing. In the figure, we recognize that there are four SRAM modules and eight Channel controllers with BISR modules, every one of which is associated with its comparing DRAM channel.

# A. Overview of Channel controller with BISR Module

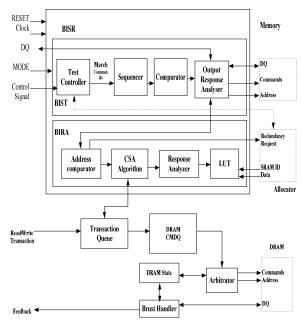

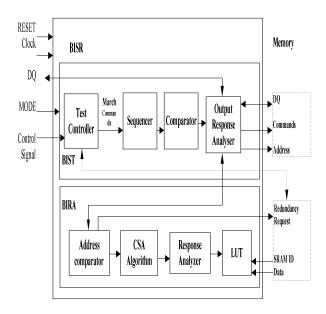

The framework of the proposed Channel controller for a lone redirect is showed up in Fig. 4. The Channel controller is made out of the BISR module, fusing BIST and Built-In Redundancy-Analysis (BIRA) module, and other average parts.

Fig 4. BOSR Channel controller of the proposed BOSR Memory architecture.

In investigate mode, the BIST module guidelines the check game plan with March computations. The BIRA module works the RA count on each event a fault is distinguished. The Allocator works of art in investigate mode is doling out the redundancies (SRAM modules) in round-robin gathering. In normal mode, the FIFO line of interchange approaches the ordinary memory Read/Write exercises. Each time a whole on (Read or Write) is scrutinized from the trade line, the BIRA module tests whether the adapt to arranges any repairing information in the LUT, and remaps it to an abundance memory thing. On the off chance that not any more, the request can be created to the DRAM Command Queue (DRAM CMDQ) and the expert will get it after the arranging crucial delay is come to. Of course, if the investigation summon manage is composed in LUT, the request might be saved to the remapped SRAM Command Queue (SRAM CMDQ),

which suggests its supply could be remapped to the relating to SRAM manage.

In Fig. 5 we show the factor by method for factor indications of the proposed BISR module in a singular Channel controller. The module is made from segments: (1) BIST, which suits of a Test Controller and a Sequencer, and (2) BIRA. The BIST circuit is a normal diagram (see, e.G., [3]). The BIRA circuit is basically a LUT further to manage examination reason, as appeared inside the decide. The point by method for point limit can be inspected underneath

Fig.5.Built in Self Repair technique in of the proposed BOSR scheme.

## **Operation of Built of self restore scheme**

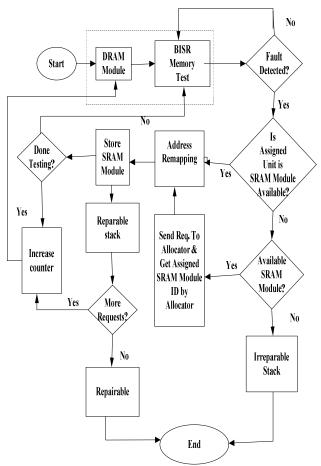

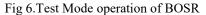

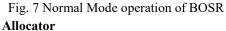

The BOSR is works first in Test mode to check the each cell of the memory. The Allocator and look into table are acting indispensable part under tight restraints mode. In the wake of completing pinch of the Test mode BOSR is works in Normal mode. The task and working of the Test Mode and Normal mode are demonstrated in stream graph fig no. 6 and fig no. 7. In test mode, each module of BISR inside the Channel controller tests its comparing memory channel on the grounds that the accept circumstances for what they are appeared in Fig. 6. The Allocator fills in as a worry generator and memory checker which decides the channels the separate redundancies are dispensed for.

In the event that blame is recognized allocator dispenses new memory district from excess module with circular robin assignment and store the fresh out of the plastic new memory region from SRAM to LUT. After of fruition of Test mode it will exchange from Test mode to consistent mode activity. Each time the Channel controller evaluations the coming asked manage from SOC as appeared inside the buoy outline in Fig.7 .In the common mode, The Allocator the gets to the LUT for confirmation of the asked for ID of DRAM Memory. In the event that address is found in LUT it'll go to SRAM module and carries on like the huge SRAM modules controller. Since the remapping records is spared in a look-into work area (LUT) in the BISR module after a blame is recognized, the adapt to examinations in the BISR modules might be expert in parallel, effectively bringing down the planning punishment all through regular get right of section to of the memory.

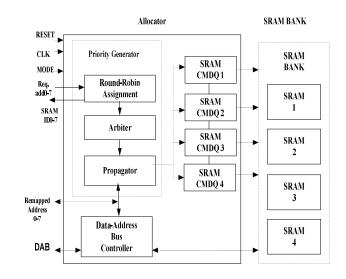

[1] The Allocator has two components of limits. One is picking which SRAM module to make utilization of while a Channel controller's BISR module requests one in test mode, the other is engineering the passage sales to the SRAM modules in conventional mode. Survey that the Channel controller's BISR modules are focused on their contrasting coordinates and depictions in parallel, openly. At the factor while more than one BISR modules requesting SRAM modules meanwhile, the Allocator need to pick and apportion the SRAM modules fittingly.

The simulation and verified effect are shown in fig. 9 of their performances. Once the realistic verification is done, the RTL mannequin is taken to the synthesis method using the Xilinx ISE instrument. This design is synthesized and its outcome were analyzed as follows.

# Note: Value Note: Value Note: <th

Fig. 9. Simulation

Desk indicates the basic comparisons with analytical difference between earlier repairing system with BOSR as show in desk as proven below in fig 10

| SPECIFICATIONS        | 2D BISR       | 3D BISR               | 3D BOSR                                             |

|-----------------------|---------------|-----------------------|-----------------------------------------------------|

| AREA                  | AREA REQUIRED | LESS AREA<br>REQUIRED | LESS AREA REQUIRD &<br>MORE UTILIZATION OF<br>SPACE |

| COMPLEXITY            | LESS COMPLEX  | MORE COMPLEX          | MORE COMPLEX THAN<br>OTHER                          |

| COST                  | COST IS MORE  | COST<br>EFFECTIVE     | COST EFFECTIVE                                      |

| DELAY                 | DELAY IS LESS | DELAY IS LESS         | DELAY IS MORE                                       |

| REPAIR<br>TECHNIQUE   | E-FUSE, LAZER | REDUNDANCY<br>E-FUSE  | EFFECTIVE<br>REDUNDANCY<br>TECHNIQUE                |

| MEMORY<br>UTILIZATION | MIDIUM        | LARGE                 | HIGH MEMORY CUBE                                    |

| YEID                  | GOOD          | MORE THAN 3D          | HIGH                                                |

|                       |               |                       |                                                     |

Fig. 10. Comparison

## **V CONCLUSION**

We propose the BOSR building with BISR plan on the controller arrange for channel-headquartered 3D memory to update the last thing yield, after the stacking of memory chomps the soil and securing of a memory 3D square to its assessing reason pass on. The BOSR designing is built from devoted Channel controllers of each channel and an Allocator to circulate and get to the redundancies on the thought process kick the pail in a considerable amount of venture modes. The BOSR circuit is shared by utilizing all memory fails horrendously, and the heaviness of realizing complex BISR circuits using development progressed for memory is released. Furthermore, the surplus memory completed on the justification bite the soil will likewise be used additional capably than those on the memory kicks the container, which are additional difficult to be shared transversely finished chomps the earth. The BISR module inside the Channel controller grasps a tedious arrangement for second memory, which is made from a test Controller and a Sequencer.

### REFERENCES

[1]"A Built-Off Self Repair Scheme for Channel Based 3D Memories" Hussan-Hung Liu, Bing-Yang Lin, Cheng-Wen Wu Wan-Ting Chiang,Mincent Lee, Hung-Chih Lin, Ching-Nen Peng and Min-Jer Wang IEEE Transactions 2017.

[2] international Roadmap for Semiconductors. 2007. To be had:

http://www.Itrs.Internet/links/2007Winter/2007\_Winter r\_Presentations/01\_ORTC\_2007\_JP.Pdf

[3] L.-T. Wang, C.-W. Wu, and X. Wen, Design for Testability: VLSI experiment principles and Architectures. San Francisco: Elsevier (Morgan Kaufmann), 2006.

[4] S.-k. Lu, Z.-Y.Wang, Y.-M.Tsai and J.-L.Chen, "efficient constructed-In Self-restore procedures for a couple of Repairable Embedded RAMs," IEEE Trans.On laptop-Aided Design of built-in Circuits and systems, vol. 31, no. 4, 2012.

[5] P. Habiby and R. N. Asli, "Design and Implementation of a new Symmetric constructed-In Redundancy Analyzer," in Proc. IntSymp.Sixteenth computer structure and Digital techniques (CADS), 2012.

[6] T.-W. Tseng, J.-F.Li, and C.-C. Hsu, "ReBISR: A reconfigurable developed-in self-repair scheme for random access reminiscences in SoCs," IEEE Trans. Very large Scale Integr.(VLSI) Syst., vol. 18, no. 6, pp. 921–932, 2010.

[7] M. Lee and C.-W. Wu, "process for repairing reminiscence and approach," U.S. Patent 20090119537, 2009.

[8] M.-S. Lee, L.-M.Denq, and C.-W. Wu, "BRAINS+: A memory built-in self-repair generator," in Proc. 1st VTTW, Paper 1.2, 2007.

[9] S.-k. Lu, C.-L.Yang, Y.-C.Hsiao, and C.-W.Wu, "efficient BISR tactics for embedded memories due to the fact that cluster faults," IEEE Trans. Very colossal Scale Integr. (VLSI) Syst., vol. 18, no. 2, pp. 184–193, 2010.

[10] P. Ohler, S. Hellebrand, and H. J. Wunderlich, "An integrated built-in test and repair technique for memories with 2-D redundancy," in Proc. 12th IEEE European test Symp.(ETS), pp. 91–ninety six, 2007.

[11]. "Hybrid Memory Cube (HMC) DRAM", HMC Consortium, 2014

[12] J. Lee, ok. Park, and S. Kang, "An subject-effective constructed-in redundancy evaluation for embedded reminiscences with top-quality repair rate using 2-D redundancy," in Proc. SoC Design convention (ISOCC), pp. 353–356, 2009

[13] K. Jamal, P. Srihari, K. Manjunatha Chari, B. Sabitha "Low Power Test Pattern Generation Using Test-Per-Scan Technique for BIST Implementation "ARPN Journal of Engineering and Applied Sciences (ISSN 1819-6608) (VOL. 13, NO. 8, APRIL 2018).

[14] K.Jamal, Dr.P.Sri hari, G Kanakasri "Test Vector Generation using Genetic Algorithm for Fault Tolerant Systems" *International Journal of* Control Theory *and Applications* (IJCTA), 9(12), 2016, pp. 5591-5598.

[15] K.Jamal, Dr.P.Sri hari "Low Power TPC using BSLFSR" International Journal of Engineering and Technology (IJET), Vol 8 No 2 Apr-May 2016. Page no.759.

[16] K.Jamal, Dr.P.Sri hari "Analysis of Test Sequence Generators for Built-In Self-Test Implementation" 2<sup>nd</sup> International Conference on Advanced Computing and Communication Systems (*ICACCS* -2015, ISSN: 978-1-4799-6438-3/15/\$31.00 ©2015 IEEE) Jan. 05 – 07, 2015.